13 | 加法器:如何像搭乐高一样搭电路(上)?

该思维导图由 AI 生成,仅供参考

异或门和半加器

- 深入了解

- 翻译

- 解释

- 总结

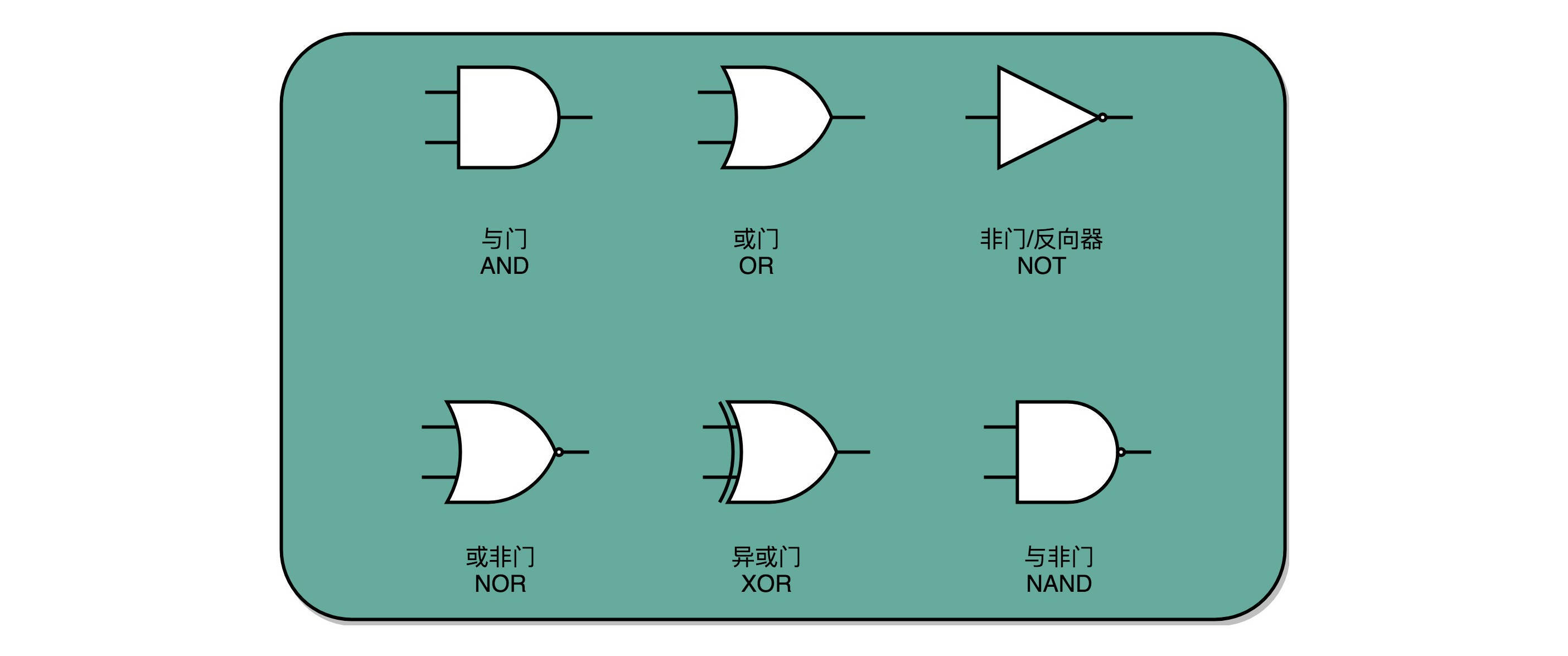

本文深入介绍了通过门电路搭建加法器的原理和方法。作者首先解释了基本的门电路,如“与(AND)”“或(OR)”“NOT(非)”和“异或(XOR)”,并阐述了它们在计算机硬件中的重要性。接着,详细讲解了半加器和全加器的设计原理,以及如何通过组合多个全加器来实现多位数的加法运算。通过生动的比喻和逻辑推理,读者能够清晰地理解门电路如何实现加法运算,以及全加器在计算机硬件中的重要作用。文章还提到了计算机设计中的分层思想,从简单到复杂逐层搭建功能组件的重要性。此外,还提到了实际CPU中使用的加法器与讲解的电路有所差别,以及对有符号数的加法器实现和补码表示的讨论。总的来说,本文适合对计算机硬件感兴趣的读者阅读,能够帮助他们快速了解门电路搭建加法器的原理和方法。

《深入浅出计算机组成原理》,新⼈⾸单¥68

全部留言(65)

- 最新

- 精选

不记年基本电路>门电路>全加器>加法器,经历了三层的封装,分层可以带来很多好处,但经过这么多层的封装是不是也带来了性能的损耗,所以我想对于像加法器这样经常用到的电路,可不可以打破分层,直接通过最底层的电路来实现,以达到性能的最优呢。在进一步,性能和封装之间是否也存在着取舍呢

不记年基本电路>门电路>全加器>加法器,经历了三层的封装,分层可以带来很多好处,但经过这么多层的封装是不是也带来了性能的损耗,所以我想对于像加法器这样经常用到的电路,可不可以打破分层,直接通过最底层的电路来实现,以达到性能的最优呢。在进一步,性能和封装之间是否也存在着取舍呢作者回复: 不记年同学你好, 你的思考很对,实际的加法器,并不是由全加器串联组成的,在14讲里面我们可以看到为了减少门延迟的损失,实际高位的计算结果直接来自低位的组合电路里面的输入。 封装意味着我们提供了更多的“简单电路”或者说“简单指令”来操作。但这也意味着同样复杂的操作需要更多条指令。 这个也是为什么在计算机体系结构里面会有 RISC 和 CISC 这样的复杂/精简 指令之争。

2019-05-27564 张立昊Leon负数用补码表示的话加法就和正数的加法没什么区别了,只是结果如果是负数的话,也是补码。发生溢出会有问题,最高位符号有可能会变,需要额外的标记位

张立昊Leon负数用补码表示的话加法就和正数的加法没什么区别了,只是结果如果是负数的话,也是补码。发生溢出会有问题,最高位符号有可能会变,需要额外的标记位作者回复: 👍

2019-05-26446 kdb_reboot这部分就是本科学的数电了

kdb_reboot这部分就是本科学的数电了作者回复: 👍

2019-05-2615 奕我们仍然是从左到右,一位一位进行计算,只是把从逢 10 进 1 变成逢 2 进 1。 这里不应该是从右往左运算吗?

奕我们仍然是从左到右,一位一位进行计算,只是把从逢 10 进 1 变成逢 2 进 1。 这里不应该是从右往左运算吗?作者回复: 一步同学你好, 谢谢指出,的确是从右到左计算,我修改一下。

2019-05-2414 玉琢天窗老师,要想自己搭建一个电路实现1+1,需要哪些材料呢

玉琢天窗老师,要想自己搭建一个电路实现1+1,需要哪些材料呢作者回复: 如果是写程序模拟的话有很多办法,比如有人用Minecraft 做了一个虚拟的CPU http://mc.163.com/2017/04/07/25535_682214.html 如果是硬件,如果只是为了体验,最简单的办法是用电路绘画导电笔直接在纸上画了来体验一下 或者也可以去淘宝上买个组合电路套件自己来搭一下。

2019-09-1147 南山打卡,5月24日03:45,坚持完整的学到底~

南山打卡,5月24日03:45,坚持完整的学到底~作者回复: 加油

2019-05-247 ldd课后思考: 补码表示下,加法器也是可以正常运行的;因为补码的发明就是为了方便正负数的二进制计算。 正数+负数是不会溢出的,所以加法器可以直接忽略最左边的进位; 但是补码计算,还是会出现溢出的情况的,比如:假设二进制位数是4位,-8-2=6;7+2=-1 就算是溢出了; 那么还是需要最右边的输出来判断是否溢出的: 假设最右边的输入为a、b,输出为c,那么溢出位可以为 (~(a&b)) & c & (~(a&b)),输出为1,就代表溢出了,否则就是未溢出。 不知道思考的对不对,有不对的地方,望老师指出。

ldd课后思考: 补码表示下,加法器也是可以正常运行的;因为补码的发明就是为了方便正负数的二进制计算。 正数+负数是不会溢出的,所以加法器可以直接忽略最左边的进位; 但是补码计算,还是会出现溢出的情况的,比如:假设二进制位数是4位,-8-2=6;7+2=-1 就算是溢出了; 那么还是需要最右边的输出来判断是否溢出的: 假设最右边的输入为a、b,输出为c,那么溢出位可以为 (~(a&b)) & c & (~(a&b)),输出为1,就代表溢出了,否则就是未溢出。 不知道思考的对不对,有不对的地方,望老师指出。作者回复: 我不知道我有没有准确理解你的意思 两个负数相加,是否溢出,其实不是看最后多出来的进位的信号。而是也要看计算结果的最高位是1还是0 如果两个输入的高位是1而输出的高位是0,那么就溢出了,如果输出的高位还是1就没有溢出。 你这里的a,b,c是不是指输入a,b和输出c的左侧的高位(不是进位的溢出位)?我的理解没有错吧?

2019-05-2726 supermouse老师您好!请问「与非门」、「或非门」是将「与门」、「或门」计算得到的结果取反吗?

supermouse老师您好!请问「与非门」、「或非门」是将「与门」、「或门」计算得到的结果取反吗?作者回复: 是的,就是把与门和或门的真值表取反

2019-05-266 小海海思考题: 反向推导,补码的设计本来就是要解决正数加负数的问题,使之可以当作普通的加法来进位即可,所以文章里的加法器模型应该是可以的

小海海思考题: 反向推导,补码的设计本来就是要解决正数加负数的问题,使之可以当作普通的加法来进位即可,所以文章里的加法器模型应该是可以的作者回复: 回答正确,不过可以再想想补码情况下,如何处理溢出呢?

2019-05-245 铁皮课后思考题: 用补码表示的话,这个加法器应该可以实现正数加负数。 最左端如有溢出位的情况去掉就可以

铁皮课后思考题: 用补码表示的话,这个加法器应该可以实现正数加负数。 最左端如有溢出位的情况去掉就可以作者回复: 是的,不过可以思考一下两个负数的相加或者整数的相加是否也会溢出?怎么通过电路来告诉大家是发生了溢出?

2019-05-244